Pengoptimuman Circuit kuantum

Toshinari Itoko (21 Jun 2024)

Muat turun pdf kuliah asal. Perhatikan bahawa beberapa coretan kod mungkin sudah lapuk kerana ini adalah imej statik.

Anggaran masa QPU untuk menjalankan eksperimen ini ialah 15 s.

(Nota: Beberapa sel dalam bahagian 2 disalin daripada notebook "Qiskit Deep dive", ditulis oleh Matthew Treinish (penyelenggara Qiskit))

# Added by doQumentation — required packages for this notebook

!pip install -q qiskit qiskit-aer qiskit-ibm-runtime

# !pip install 'qiskit[visualization]'

# !pip install qiskit_ibm_runtime qiskit_aer

# !pip install jupyter

# !pip install matplotlib pylatexenc pydot pillow

import qiskit

qiskit.__version__

'2.0.2'

import qiskit_ibm_runtime

qiskit_ibm_runtime.__version__

'0.40.1'

import qiskit_aer

qiskit_aer.__version__

'0.17.1'

1. Pengenalan

Pelajaran ini akan membincangkan beberapa aspek pengoptimuman Circuit dalam pengkomputeran kuantum. Khususnya, kita akan melihat nilai pengoptimuman Circuit dengan menggunakan tetapan pengoptimuman yang terbina dalam Qiskit. Kemudian kita akan mendalami lebih lanjut dan melihat apa yang boleh kamu lakukan sebagai pakar dalam bidang aplikasi tertentu untuk membina Circuit dengan cara yang bijak. Akhir sekali, kita akan mengkaji dengan teliti apa yang berlaku semasa transpilasi yang membantu kita mengoptimumkan Circuit.

2. Pengoptimuman Circuit itu penting

Kita mula-mula membandingkan keputusan daripada menjalankan Circuit persediaan keadaan GHZ 5-Qubit () dengan dan tanpa pengoptimuman.

from qiskit.circuit import QuantumCircuit

from qiskit.transpiler.preset_passmanagers import generate_preset_pass_manager

from qiskit.primitives import BackendSamplerV2 as Sampler

from qiskit_ibm_runtime.fake_provider import FakeBrisbane

backend = FakeBrisbane()

Kita mula-mula menggunakan Circuit GHZ yang disintesis secara naif seperti berikut.

num_qubits = 5

ghz_circ = QuantumCircuit(num_qubits)

ghz_circ.h(0)

[ghz_circ.cx(0, i) for i in range(1, num_qubits)]

ghz_circ.measure_all()

ghz_circ.draw("mpl")

2.1 Tahap pengoptimuman

Terdapat 4 optimization_level yang tersedia dari 0–3. Semakin tinggi tahap pengoptimuman, semakin banyak usaha pengiraan yang digunakan untuk mengoptimumkan Circuit. Tahap 0 tidak melakukan sebarang pengoptimuman dan hanya melakukan jumlah kerja minimum untuk membolehkan Circuit dijalankan pada backend yang dipilih. Tahap 3 menggunakan usaha (dan biasanya masa jalan) yang paling banyak untuk cuba mengoptimumkan Circuit. Tahap 1 ialah tahap pengoptimuman lalai.

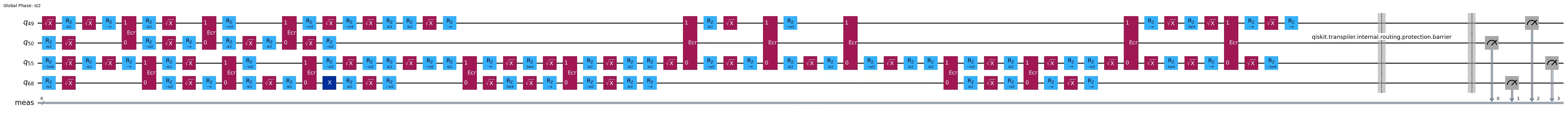

Kita mentranspil Circuit tanpa pengoptimuman (optimization_level=0) dan dengan pengoptimuman (optimization_level=2). Kita dapat melihat perbezaan besar dalam panjang Circuit yang ditranspil.

pm0 = generate_preset_pass_manager(

optimization_level=0, backend=backend, seed_transpiler=777

)

pm2 = generate_preset_pass_manager(

optimization_level=2, backend=backend, seed_transpiler=777

)

circ0 = pm0.run(ghz_circ)

circ2 = pm2.run(ghz_circ)

print("optimization_level=0:")

display(circ0.draw("mpl", idle_wires=False, fold=-1))

print("optimization_level=2:")

display(circ2.draw("mpl", idle_wires=False, fold=-1))

optimization_level=0:

optimization_level=2:

2.2 Latihan

Cuba optimization_level=1 juga dan bandingkan Circuit yang dihasilkan dengan dua di atas. Cuba dengan mengubah suai kod di atas.

Penyelesaian:

pm1 = generate_preset_pass_manager(

optimization_level=1, backend=backend, seed_transpiler=777

)

circ1 = pm1.run(ghz_circ)

print("optimization_level=1:")

display(circ1.draw("mpl", idle_wires=False, fold=-1))

optimization_level=1:

Jalankan pada backend palsu (simulasi berbising). Lihat Lampiran 1 untuk cara menjalankan pada backend sebenar.

# run the circuits on the fake backend (noisy simulator)

sampler = Sampler(backend=backend)

job = sampler.run([circ0, circ2], shots=10000)

print(f"Job ID: {job.job_id()}")

Job ID: 93a4ac70-e3ea-44ad-aea9-5045840c9076

# get results

result = job.result()

unoptimized_result = result[0].data.meas.get_counts()

optimized_result = result[1].data.meas.get_counts()

from qiskit.visualization import plot_histogram

# plot

sim_result = {"0" * 5: 0.5, "1" * 5: 0.5}

plot_histogram(

[result for result in [sim_result, unoptimized_result, optimized_result]],

bar_labels=False,

legend=[

"ideal",

"no optimization",

"with optimization",

],

)

3. Sintesis Circuit itu penting

Seterusnya kita membandingkan keputusan daripada menjalankan dua Circuit persediaan keadaan GHZ 5-Qubit () yang disintesis secara berbeza.

# Original GHZ circuit (naive synthesis)

ghz_circ.draw("mpl")

# A cleverly-synthesized GHZ circuit

ghz_circ2 = QuantumCircuit(5)

ghz_circ2.h(2)

ghz_circ2.cx(2, 1)

ghz_circ2.cx(2, 3)

ghz_circ2.cx(1, 0)

ghz_circ2.cx(3, 4)

ghz_circ2.measure_all()

ghz_circ2.draw("mpl")

# transpile both with the same optimization level 2

circ_org = pm2.run(ghz_circ)

circ_new = pm2.run(ghz_circ2)

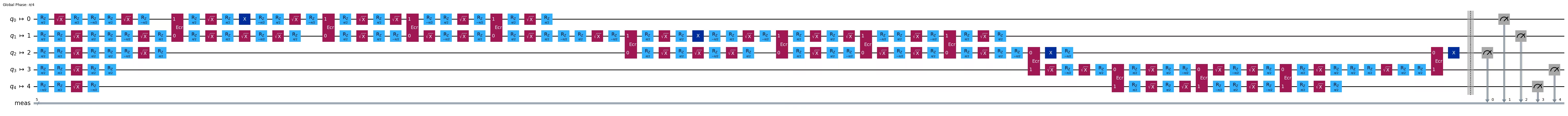

print("original synthesis:")

display(circ_org.draw("mpl", idle_wires=False, fold=-1))

print("new synthesis:")

display(circ_new.draw("mpl", idle_wires=False, fold=-1))

original synthesis:

new synthesis:

Sintesis baru menghasilkan Circuit yang lebih cetek. Mengapa?

Ini kerana Circuit baru boleh diletakkan pada Qubit yang bersambung secara linear, jadi pada graf gandingan heavy-hexagon IBM® Brisbane juga, manakala Circuit asal memerlukan ketersambungan berbentuk bintang (nod berdarjah-4) dan oleh itu tidak boleh diletakkan pada graf gandingan heavy-hex, yang mempunyai nod dengan darjah paling tinggi 3. Hasilnya, Circuit asal memerlukan penghala Qubit yang menambah Gate SWAP, meningkatkan bilangan Gate.

Apa yang kita lakukan dalam Circuit baru boleh dilihat sebagai sintesis Circuit "sedar kekangan gandingan" secara manual. Dengan kata lain: menyelesaikan sintesis Circuit dan pemetaan Circuit secara serentak secara manual.

# run the circuits

sampler = Sampler(backend=backend)

job = sampler.run([circ_org, circ_new], shots=10000)

print(f"Job ID: {job.job_id()}")

Job ID: 19d635b0-4d8b-44c2-a76e-49e4b9078b1b

# get results

result = job.result()

synthesis_org_result = result[0].data.meas.get_counts()

synthesis_new_result = result[1].data.meas.get_counts()

# plot

sim_result = {"0" * 5: 0.5, "1" * 5: 0.5}

plot_histogram(

[

result

for result in [

sim_result,

unoptimized_result,

synthesis_org_result,

synthesis_new_result,

]

],

bar_labels=False,

legend=[

"ideal",

"no optimization",

"synthesis_org",

"synthesis_new",

],

)

Secara umum, sintesis Circuit bergantung pada aplikasi dan agak sukar bagi perisian untuk merangkumi semua aplikasi yang mungkin. Transpiler Qiskit kebetulan tidak mempunyai fungsi untuk mensintesis Circuit persediaan keadaan GHZ. Dalam kes sedemikian, sintesis Circuit secara manual seperti yang ditunjukkan di atas patut dipertimbangkan.

Dalam bahagian ini, kita mengkaji dengan teliti cara Transpiler Qiskit berfungsi menggunakan Circuit contoh mainan berikut.

# Build a toy example circuit

from math import pi

import itertools

from qiskit.circuit import QuantumCircuit

from qiskit.circuit.library import excitation_preserving

circuit = QuantumCircuit(4, name="Example circuit")

circuit.append(excitation_preserving(4, reps=1, flatten=True), range(4))

circuit.measure_all()

value_cycle = itertools.cycle([0, pi / 4, pi / 2, 3 * pi / 4, pi, 2 * pi])

circuit.assign_parameters(

[x[1] for x in zip(range(len(circuit.parameters)), value_cycle)], inplace=True

)

circuit.draw("mpl")

3.1 Lukis keseluruhan aliran transpilasi Qiskit

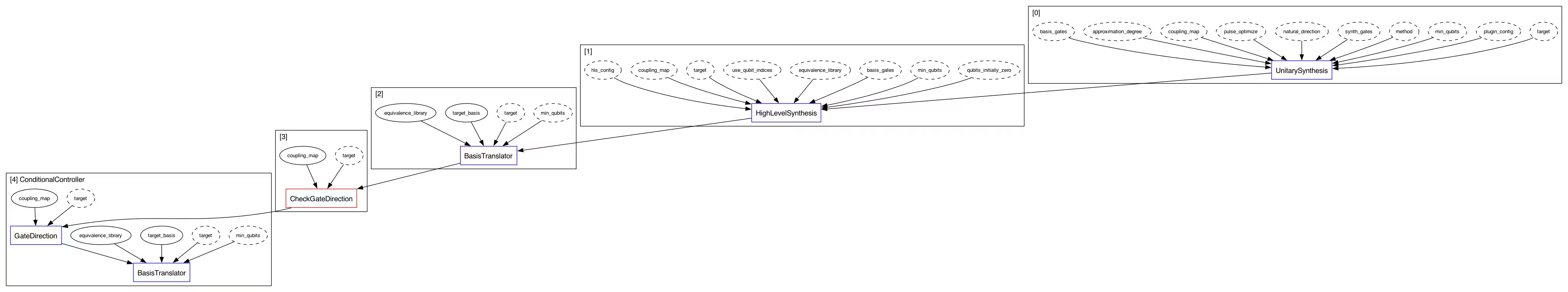

Kita mengkaji pas transpiler (tugas) untuk optimization_level=1.

from qiskit.transpiler.preset_passmanagers import generate_preset_pass_manager

# There is no need to read this entire image, but this outputs all the steps in the transpile() call

# for optimization level 1

pm = generate_preset_pass_manager(1, backend, seed_transpiler=42)

pm.draw()

Aliran terdiri daripada enam peringkat:

print(pm.stages)

('init', 'layout', 'routing', 'translation', 'optimization', 'scheduling')

3.2 Lukis peringkat individu

Pertama, jom lukis semua tugas (pas transpiler) yang dilakukan dalam peringkat init.

pm.init.draw()

Kita boleh menjalankan setiap peringkat secara individu. Jom jalankan peringkat init untuk Circuit kita. Dengan mengaktifkan logger, kita boleh melihat butiran pelaksanaan.

import logging

logger = logging.getLogger()

logger.setLevel("INFO")

init_out = pm.init.run(circuit)

init_out.draw("mpl", fold=-1)

INFO:qiskit.passmanager.base_tasks:Pass: UnitarySynthesis - 0.03576 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: HighLevelSynthesis - 0.16618 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: BasisTranslator - 0.07176 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: InverseCancellation - 0.27299 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: ContractIdleWiresInControlFlow - 0.00811 (ms)

3.3 Latihan

Lukis pas peringkat layout dan jalankan peringkat itu untuk Circuit output peringkat init (init_out), dengan mengubah suai sel yang digunakan di atas.

Penyelesaian:

display(pm.layout.draw())

layout_out = pm.layout.run(init_out)

layout_out.draw("mpl", idle_wires=False, fold=-1)

INFO:qiskit.passmanager.base_tasks:Pass: SetLayout - 0.01001 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: TrivialLayout - 0.07129 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: CheckMap - 0.08917 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: VF2Layout - 1.24431 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: BarrierBeforeFinalMeasurements - 0.02599 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: SabreLayout - 5.11169 (ms)

Lakukan perkara yang sama untuk peringkat translation.

Penyelesaian:

display(pm.translation.draw())

basis_out = pm.translation.run(layout_out)

basis_out.draw("mpl", idle_wires=False, fold=-1)

INFO:qiskit.passmanager.base_tasks:Pass: UnitarySynthesis - 0.03386 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: HighLevelSynthesis - 0.02718 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: BasisTranslator - 2.64192 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: CheckGateDirection - 0.02217 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: GateDirection - 0.36502 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: BasisTranslator - 0.64778 (ms)

Nota: Setiap peringkat individu tidak selalu boleh dijalankan secara bebas (kerana sesetengahnya perlu membawa maklumat daripada satu peringkat sebelumnya).

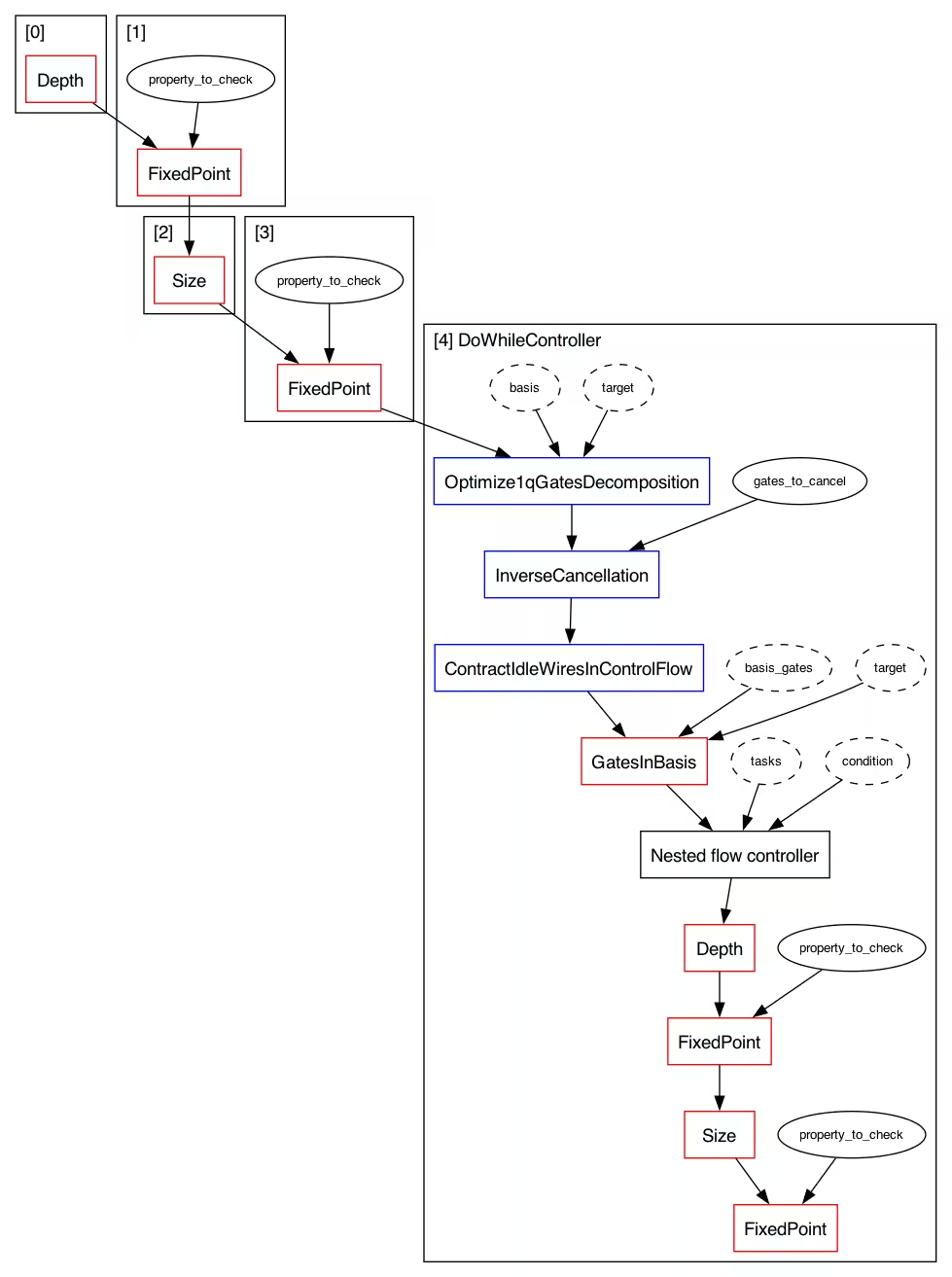

3.4 Peringkat Pengoptimuman

Peringkat lalai terakhir dalam saluran paip ialah pengoptimuman. Selepas kita menyematkan Circuit untuk sasaran, Circuit telah berkembang dengan cukup besar. Kebanyakannya disebabkan oleh ketidakcekapan dalam hubungan kesetaraan daripada terjemahan asas dan penyisipan swap. Peringkat pengoptimuman digunakan untuk cuba meminimumkan saiz dan kedalaman Circuit. Ia menjalankan satu siri pas dalam gelung do while sehingga mencapai output yang stabil.

# pm.pre_optimization.draw()

pm.optimization.draw()

logger = logging.getLogger()

logger.setLevel("INFO")

opt_out = pm.optimization.run(basis_out)

INFO:qiskit.passmanager.base_tasks:Pass: Depth - 0.30112 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.03195 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Size - 0.01216 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.01001 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Optimize1qGatesDecomposition - 0.63729 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: InverseCancellation - 0.41723 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: ContractIdleWiresInControlFlow - 0.01192 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: GatesInBasis - 0.05484 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Depth - 0.08583 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.20599 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Size - 0.00787 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.00715 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Optimize1qGatesDecomposition - 0.16809 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: InverseCancellation - 0.17190 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: ContractIdleWiresInControlFlow - 0.00691 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: GatesInBasis - 0.02408 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Depth - 0.04935 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.00525 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: Size - 0.00620 (ms)

INFO:qiskit.passmanager.base_tasks:Pass: FixedPoint - 0.00286 (ms)

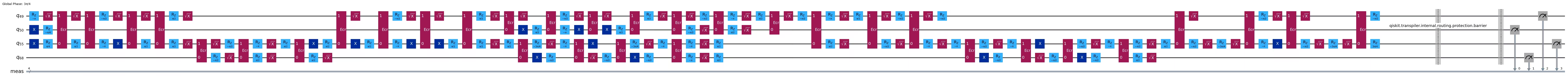

opt_out.draw("mpl", idle_wires=False, fold=-1)

4. Contoh mendalam

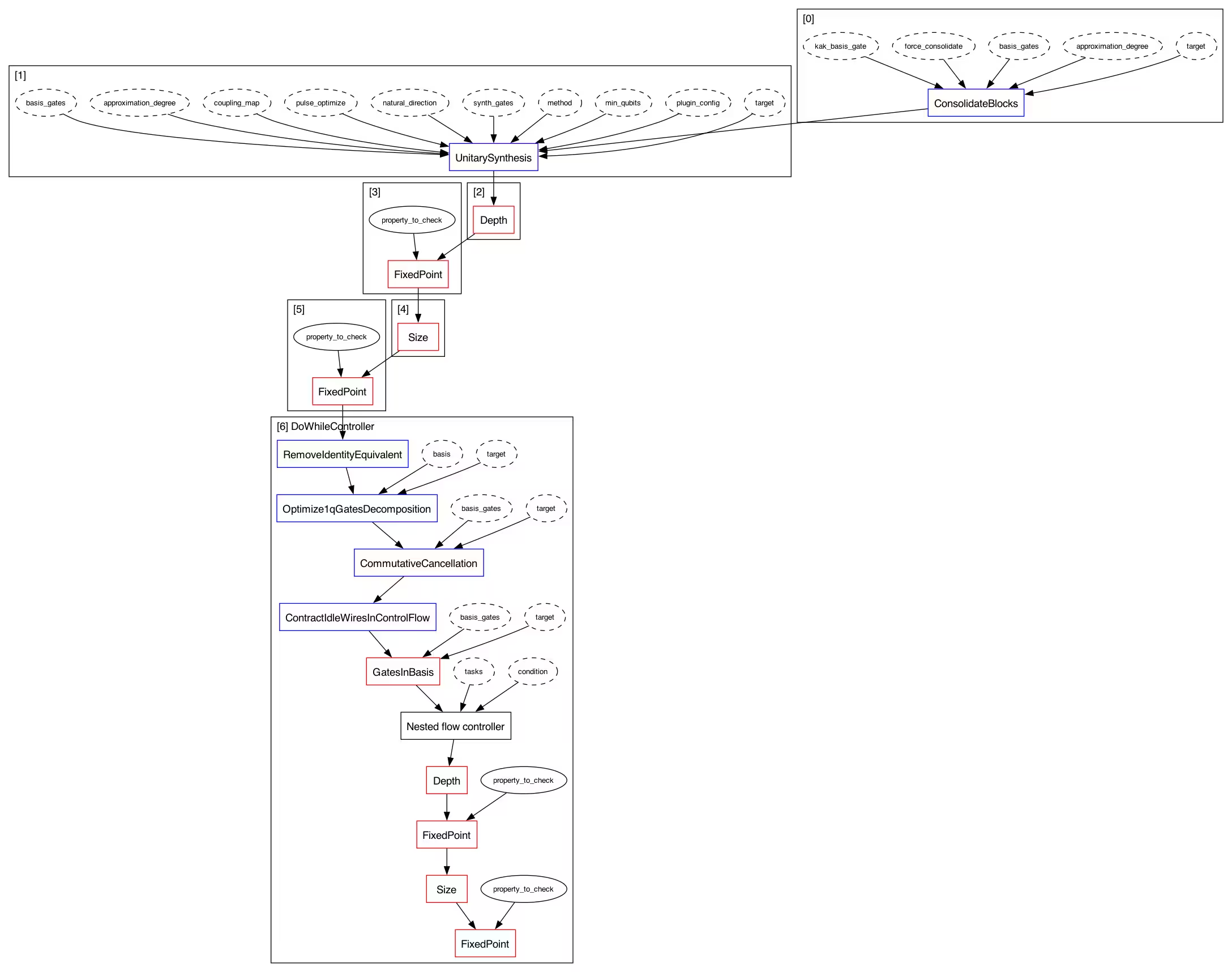

4.1 Pengoptimuman blok dua-Qubit menggunakan sintesis kesatuan dua-Qubit

Untuk tahap 2 dan 3, kita ada lebih banyak pas (Collect2qBlocks, ConsolidateBlocks, UnitarySynthesis) untuk pengoptimuman yang lebih mendalam, iaitu pengoptimuman blok dua-Qubit. (Bandingkan aliran peringkat pengoptimuman untuk tahap 2 dengan aliran tahap 1 di atas)

Pengoptimuman blok dua-Qubit terdiri daripada dua langkah: Mengumpul dan menyatukan blok 2-Qubit, serta menyintesis matriks kesatuan 2-Qubit.

pm2 = generate_preset_pass_manager(2, backend, seed_transpiler=42)

pm2.optimization.draw()

from qiskit.transpiler import PassManager

from qiskit.transpiler.passes import (

Collect2qBlocks,

ConsolidateBlocks,

UnitarySynthesis,

)

# Collect 2q blocks and consolidate to unitary when we expect that we can reduce the 2q gate count for that unitary

consolidate_pm = PassManager(

[

Collect2qBlocks(),

ConsolidateBlocks(target=backend.target),

]

)

display(basis_out.draw("mpl", idle_wires=False, fold=-1))

consolidated = consolidate_pm.run(basis_out)

consolidated.draw("mpl", idle_wires=False, fold=-1)

# Synthesize unitaries

UnitarySynthesis(target=backend.target)(consolidated).draw(

"mpl", idle_wires=False, fold=-1

)

logger.setLevel("WARNING")

Kita telah lihat dalam Bahagian 2 bahawa aliran pengkompil kuantum sebenar tidak semudah itu dan terdiri daripada banyak pas (tugas). Ini terutamanya disebabkan oleh kejuruteraan perisian yang diperlukan untuk memastikan prestasi bagi pelbagai Circuit aplikasi dan kebolehselenggaraan perisian. Transpiler Qiskit akan berfungsi dengan baik dalam kebanyakan kes, tetapi jika Circuit kamu tidak dioptimumkan dengan baik oleh Transpiler Qiskit, ini boleh menjadi peluang yang baik untuk menyelidik pengoptimuman Circuit khusus aplikasi kamu sendiri seperti yang ditunjukkan dalam Bahagian 1. Teknologi Transpiler terus berkembang, sumbangan R&D kamu sangat dialu-alukan.

from qiskit.circuit import QuantumCircuit

from qiskit_ibm_runtime import QiskitRuntimeService, Sampler

service = QiskitRuntimeService()

backend = service.backend("ibm_brisbane")

sampler = Sampler(backend)

circ = QuantumCircuit(3)

circ.ccx(0, 1, 2)

circ.measure_all()

circ.draw("mpl")

sampler.run([circ]) # IBMInputValueError will be raised

4.2 Pengoptimuman Circuit penting

Pertama, kita bandingkan keputusan menjalankan Circuit persediaan keadaan GHZ 5-Qubit () dengan dan tanpa pengoptimuman.

from qiskit.circuit import QuantumCircuit

from qiskit.transpiler.preset_passmanagers import generate_preset_pass_manager

from qiskit_ibm_runtime import QiskitRuntimeService, Sampler

service = QiskitRuntimeService()

# backend = service.backend('ibm_brisbane')

backend = service.least_busy(

operational=True, simulator=False, min_num_qubits=127

) # Eagle

backend

Pertama, kita gunakan Circuit GHZ yang disintesis secara naif seperti berikut.

num_qubits = 5

ghz_circ = QuantumCircuit(num_qubits)

ghz_circ.h(0)

[ghz_circ.cx(0, i) for i in range(1, num_qubits)]

ghz_circ.measure_all()

ghz_circ.draw("mpl")

Kita transpilasi Circuit tanpa pengoptimuman (optimization_level=0) dan dengan pengoptimuman (optimization_level=2).

Seperti yang dapat dilihat, terdapat perbezaan besar dalam panjang Circuit yang telah ditranspilasi.

pm0 = generate_preset_pass_manager(

optimization_level=0, backend=backend, seed_transpiler=777

)

pm2 = generate_preset_pass_manager(

optimization_level=2, backend=backend, seed_transpiler=777

)

circ0 = pm0.run(ghz_circ)

circ2 = pm2.run(ghz_circ)

print("optimization_level=0:")

display(circ0.draw("mpl", idle_wires=False, fold=-1))

print("optimization_level=2:")

display(circ2.draw("mpl", idle_wires=False, fold=-1))

optimization_level=0:

optimization_level=2:

# run the circuits

sampler = Sampler(backend)

job = sampler.run([circ0, circ2], shots=10000)

job_id = job.job_id()

print(f"Job ID: {job_id}")

Job ID: d13rnnemya70008ek1zg

# REPLACE WITH YOUR OWN JOB IDS

job = service.job(job_id)

# get results

result = job.result()

unoptimized_result = result[0].data.meas.get_counts()

optimized_result = result[1].data.meas.get_counts()

from qiskit.visualization import plot_histogram

# plot

sim_result = {"0" * 5: 0.5, "1" * 5: 0.5}

plot_histogram(

[result for result in [sim_result, unoptimized_result, optimized_result]],

bar_labels=False,

legend=[

"ideal",

"no optimization",

"with optimization",

],

)

4.3 Sintesis Circuit penting

Seterusnya, kita bandingkan keputusan menjalankan dua Circuit persediaan keadaan GHZ 5-Qubit () yang disintesis secara berbeza.

# Original GHZ circuit (naive synthesis)

ghz_circ.draw("mpl")

# A better GHZ circuit (smarter synthesis), you learned in a previous lecture

ghz_circ2 = QuantumCircuit(5)

ghz_circ2.h(2)

ghz_circ2.cx(2, 1)

ghz_circ2.cx(2, 3)

ghz_circ2.cx(1, 0)

ghz_circ2.cx(3, 4)

ghz_circ2.measure_all()

ghz_circ2.draw("mpl")

circ_org = pm2.run(ghz_circ)

circ_new = pm2.run(ghz_circ2)

print("original synthesis:")

display(circ_org.draw("mpl", idle_wires=False, fold=-1))

print("new synthesis:")

display(circ_new.draw("mpl", idle_wires=False, fold=-1))

original synthesis:

new synthesis:

# run the circuits

sampler = Sampler(backend)

job = sampler.run([circ_org, circ_new], shots=10000)

job_id = job.job_id()

print(f"Job ID: {job_id}")

Job ID: d13rp283grvg008j12fg

# REPLACE WITH YOUR OWN JOB IDS

job = service.job(job_id)

# get results

result = job.result()

synthesis_org_result = result[0].data.meas.get_counts()

synthesis_new_result = result[1].data.meas.get_counts()

# plot

sim_result = {"0" * 5: 0.5, "1" * 5: 0.5}

plot_histogram(

[result for result in [sim_result, synthesis_org_result, synthesis_new_result]],

bar_labels=False,

legend=[

"ideal",

"synthesis_org",

"synthesis_new",

],

)

4.4 Penguraian Gate 1-Qubit Umum

from qiskit import QuantumCircuit, transpile

from qiskit.circuit import Parameter

from qiskit.circuit.library.standard_gates import UGate

phi, theta, lam = Parameter("φ"), Parameter("θ"), Parameter("λ")

qc = QuantumCircuit(1)

qc.append(UGate(theta, phi, lam), [0])

qc.draw(output="mpl")

transpile(qc, basis_gates=["rz", "sx"]).draw(output="mpl")

4.5 Pengoptimuman Blok 1-Qubit

from qiskit import QuantumCircuit

qc = QuantumCircuit(1)

qc.x(0)

qc.y(0)

qc.z(0)

qc.rx(1.23, 0)

qc.ry(1.23, 0)

qc.rz(1.23, 0)

qc.h(0)

qc.s(0)

qc.t(0)

qc.sx(0)

qc.sdg(0)

qc.tdg(0)

qc.draw(output="mpl")

from qiskit.quantum_info import Operator

Operator(qc)

Operator([[ 0.45292511-0.57266982j, -0.66852684-0.14135058j],

[ 0.14135058+0.66852684j, -0.57266982+0.45292511j]],

input_dims=(2,), output_dims=(2,))

from qiskit import transpile

qc_opt = transpile(qc, basis_gates=["rz", "sx"])

qc_opt.draw(output="mpl")

Operator(qc_opt)

Operator([[ 0.45292511-0.57266982j, -0.66852684-0.14135058j],

[ 0.14135058+0.66852684j, -0.57266982+0.45292511j]],

input_dims=(2,), output_dims=(2,))

Operator(qc).equiv(Operator(qc_opt))

True

4.6 Penguraian Toffoli

qc = QuantumCircuit(3)

qc.ccx(0, 1, 2)

qc.draw(output="mpl")

from qiskit import QuantumCircuit, transpile

qc = QuantumCircuit(3)

qc.ccx(0, 1, 2)

qc = transpile(qc, basis_gates=["rz", "sx", "cx"])

qc.draw(output="mpl")

4.7 Penguraian Gate CU

from qiskit.circuit.library.standard_gates import CUGate

phi, theta, lam, gamma = Parameter("φ"), Parameter("θ"), Parameter("λ"), Parameter("γ")

qc = QuantumCircuit(2)

# qc.cu(theta, phi, lam, gamma, 0, 1)

qc.append(CUGate(theta, phi, lam, gamma), [0, 1])

qc.draw(output="mpl")

from qiskit.circuit.library.standard_gates import CUGate

phi, theta, lam, gamma = Parameter("φ"), Parameter("θ"), Parameter("λ"), Parameter("γ")

qc = QuantumCircuit(2)

qc.append(CUGate(theta, phi, lam, gamma), [0, 1])

qc = transpile(qc, basis_gates=["rz", "sx", "cx"])

qc.draw(output="mpl")

4.8 CX, ECR, CZ Setara Hingga Clifford Setempat

Perhatikan bahawa (Hadamard), ( putaran-Z), ( putaran-Z), (Pauli X) semuanya adalah Gate Clifford.

qc = QuantumCircuit(2)

qc.cx(0, 1)

qc.draw(output="mpl", style="bw")

qc = QuantumCircuit(2)

qc.cx(0, 1)

transpile(qc, basis_gates=["x", "s", "h", "sdg", "ecr"]).draw(output="mpl", style="bw")

qc = QuantumCircuit(2)

qc.cx(0, 1)

transpile(qc, basis_gates=["h", "cz"]).draw(output="mpl", style="bw")

Menggunakan Gate asas 1-Qubit Backend IBM "rz", "sx" dan "x".

qc = QuantumCircuit(2)

qc.cx(0, 1)

transpile(qc, basis_gates=["rz", "sx", "x", "ecr"]).draw(output="mpl", style="bw")

qc = QuantumCircuit(2)

qc.cx(0, 1)

transpile(qc, basis_gates=["rz", "sx", "x", "cz"]).draw(output="mpl", style="bw")

# Check Qiskit version

import qiskit

qiskit.__version__

'2.0.2'